Intel's Pat Gelsinger looks ahead Pg 28

Triple-play roadblocks: technology or competence? Pg 18

Prying Eyes investigates tech for thrifty tune-toters Pg 34

**Design Ideas** Pg 83

**VOICE OF THE ENGINEER**

100-MBPS BROADBAND:

HOW, WHY,

WHEN, AND

WHERE?

Page 48

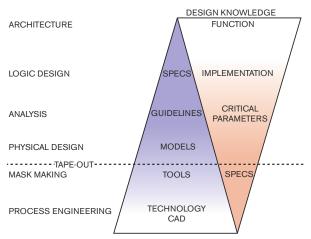

IS CHIP DESIGN DIFFERENT AFTER 90 NM?

Page 37

#### **Isolating USB**

Page 63

REDUCING GROUND BOUNCE IN DC/DC-CONVERTER APPLICATIONS

Page 73

# EXPRESSION DE PERFORMANCE...

Achieve highest system speed and better design margin with the world's first 65nm FPGAs.

Virtex<sup>™</sup>-5 FPGAs feature ExpressFabric<sup>™</sup> technology on 65nm triple-oxide process. This new fabric offers the industry's first LUT with six independent inputs for fewer logic levels, *and* advanced diagonal interconnect to enable the shortest, fastest routing. Now you can achieve 30% higher performance, while reducing dynamic power by 35% and area by 45% compared to previous generations.

# 1.4 x 1.4 x 2.4 x 1.4 x 1.4 x 1.4 x 1.6 x 1.6 x 1.6 x 1.7 Seption Point Pictor RAM 32-Tap Filter Bandwidth 750 Gbps Performance 550 MHz 750 Gbps Virtex-5 FPGAs Virtex-4 FPGAs Numbers show comparision with nearest competitor Based on competitor's published distasheet numbers Based on competitor's published distasheet numbers

#### Design systems faster than ever before

Shipping now, Virtex-5 LX is the first of four platforms optimized for logic, DSP, processing, and serial. The LX platform offers 330,000 logic cells and 1,200 user I/Os, plus hardened 550 MHz IP blocks. Build deeper FIFOs with 36 Kbit block RAMs. Achieve 1.25 Gbps on all I/Os without restrictions, and make reliable memory interfacing easier with enhanced ChipSync™ technology. Solve SI challenges and simplify PCB layout with our sparse chevron packaging. And enable greater DSP precision and dynamic range with 550 MHz, 25x18 MACs.

Visit www.xilinx.com/virtex5, view the TechOnline webcast, and give your next design the ultimate in performance.

The Ultimate System Integration Platform

FROM

CELEBORETERS

TO 7 IN PETWEEN!

625,000+ parts from a seamless linecard of over 320 top-quality manufacturers.\*

CORPORATION

1.800.344.4539 · www.digikey.com

\* New Product Added Daily!

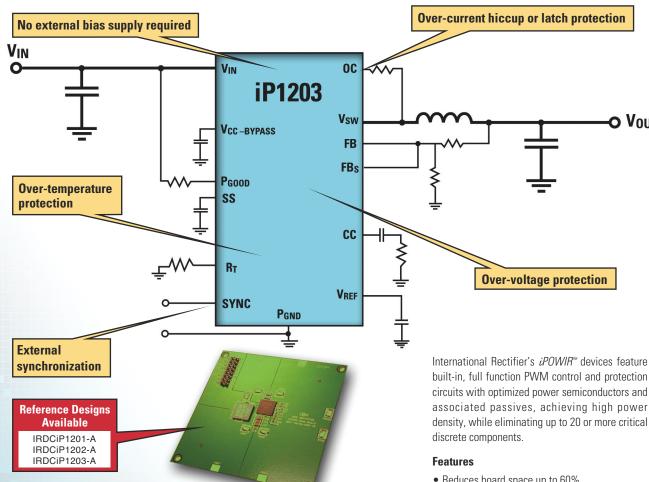

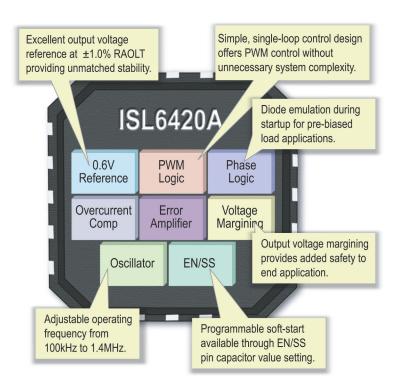

# 15A, SIMPLE, SMALL BUCK CONVERTER

iP120x Synchronous Buck Power Blocks Reduce Board Space Up to 60%

|    | Part Package |                                      | V <sub>IN</sub><br>(min/max) | V <sub>out</sub>                                                   | I <sub>оит</sub>       | Frequency    |  |

|----|--------------|--------------------------------------|------------------------------|--------------------------------------------------------------------|------------------------|--------------|--|

|    | iP1201       | BGA<br>9.25mm x<br>15.5mm x<br>2.6mm | 3.14V<br>to 5.5V             | 0.8V-2.5V for 3.3V <sub>IN</sub><br>0.8V-3.3V for 5V <sub>IN</sub> | 15A dual<br>30A single | 200 - 400kHz |  |

|    | iP1202       | BGA<br>9.25mm x<br>15.5mm x<br>2.6mm | 5.5V to<br>13.2V             | 0.8V-5V for 12V <sub>IN</sub><br>0.8V-3.3V for <6V <sub>IN</sub>   | 15A dual<br>30A single | 200 - 400kHz |  |

| NE | iP1203       | LGA<br>9mm x<br>9mm x<br>2.3mm       | 5.5V to<br>13.2V             | 0.8V-8.0V for 12V <sub>IN</sub><br>0.8V-3.3V for <6V <sub>IN</sub> | 15A single             | 200 - 400kHz |  |

iPOWIR is a trademark of International Rectifier

built-in, full function PWM control and protection circuits with optimized power semiconductors and associated passives, achieving high power density, while eliminating up to 20 or more critical

O VOUT

- Reduces board space up to 60%

- Over 90% efficient (12V<sub>IN</sub>, 3.3 V<sub>OUT</sub> @15A)

- Reduced design complexity versus discrete solutions

- Saves up to 3 months design time

- No de-rating up to 90°C PCB and case temperature

Let International Rectifier's online simulation support at mypower.irf.com and reference design kits help you with your next design.

THE POWER MANAGEMENT LEADER

#### **Back a winner!**

Atmel's ARM®-based 32-bit microcontrollers are winners. They have already picked up four prestigious awards from readers of industry leading magazines\*. Why? Because they give you exactly what you want. On-chip Flash memory. USB & Ethernet connectivity. DMA to eliminate internal bottlenecks. Supervisory functions. All this at the lowest possible power consumption and unit price, plus code compatibility across the entire product family. So, make your application a winner by backing a winner: Atmel's AT91SAM Smart ARM-based microcontrollers.

\* EEProductCenter Ultimate Product (Processor & Memory) for Q4 2004 and again for Q4 2005, Embedded Control Europe Gold Award (Micros & DSP) for H2 2005, 2006 EETimes ACE Award Ultimate Product of the Year.

Learn more about our AT91 products by visiting our web site, at www.atmel.com/ad/at91 and register to qualify for a free AT91SAM7 development kit. You will also receive an AT91 DVD with extensive product documentation, training material, application notes and code samples.

Check out Atmel's AT91 solutions at www.atmel.com/products/at91

# The Test Platform of Choice for Thousands of Companies Worldwide

Microsoft

Boeing

BAE Systems

Lockheed Martin

United States Air Force

Honeywell

Saab

**Johns Hopkins University**

Pyrex DePuy,

a Johnson & Johnson Company

Samsung

Stanford University

National Institute of

Oceanic Technology

Lund Institute of Technology

Sandia National Laboratories

Lexmark

Magneti Marelli, a Fiat company

Renault

Summitek Instruments

**United States Navy**

**United States Army**

Toshiba

Flextronics

Fiat

Niksar Australia Pty Ltd. NEC Aerospace Systems

Siemens

SELEX Sistemi Integrati

Huari Telecom

**Soliton Technologies**

**Active Signal Technologies**

PC-Based Controller

Modular Instruments DC to 6.6 GHz Rack Mount or Portable Chassis

# PXI is a modular, software-defined platform for measurement and automation systems.

- Open industry standard supported by more than 70 vendors and 1,200 products

- Highest-accuracy instruments, including the highestresolution digitizer with -120 dBc typical SFDR

- Industrial-grade, cost-effective system based on standard PC technologies

- Direct connectivity to existing instruments using GPIB, Ethernet/LAN, USB, CompactPCI, PCI, and PCI Express

- Software-defined configuration and automation with National Instruments LabVIEW and LabWindows/CVI, C/C++, NI TestStand, and Microsoft .NET

Choose from a complete set of PXI chassis, controllers, and modular instruments from NI.

| PXI Chassis                 | 3U, 6U, rack-mount, 4 to 18 slots  |

|-----------------------------|------------------------------------|

| PXI Controllers             | Remote or embedded                 |

| Digitizers/Oscilloscopes    | Up to 24 bits, 250 MS/s            |

| Signal Generators           | Up to 16 bits, 200 MS/s            |

| High-Speed Digital I/O      | Up to 400 Mb/s                     |

| RF                          | Up to 6.6 GHz, 20 MHz RTB          |

| Digital Multimeters         | Up to 7½ digits, LCR, 1,000 V      |

| Programmable Power Supplies | Up to 20 W, 16 bits                |

| Audio Analyzers             | Up to 24 bits, 500 kS/s            |

| Switches                    | Multiplexers, matrices, RF, relays |

| Multifunction I/O           | Analog I/O, digital I/O, counters  |

|                             |                                    |

To learn why each of these customers chose PXI, visit **ni.com/pxi**.

(800) 891 8841

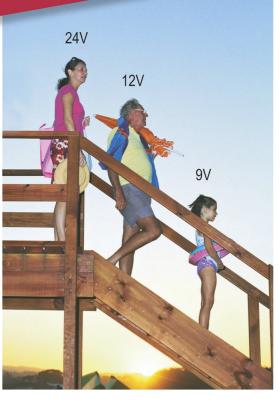

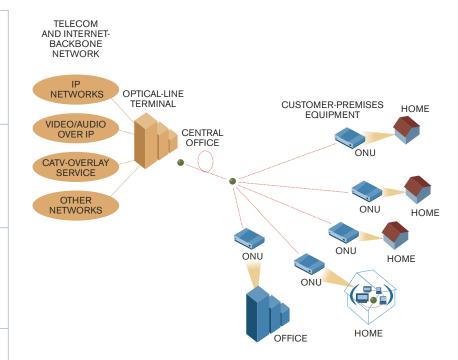

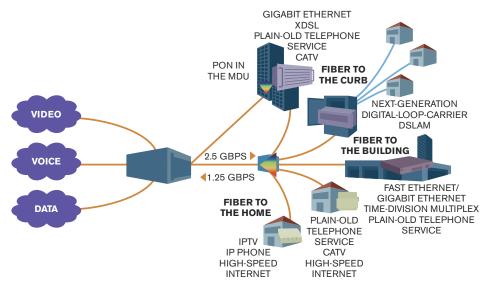

#### 100-Mbps broadband: how, why, when, and where?

A triple play of voice, video, and data moves the bandwidth target as consumers adopt HDTV and DVR technologies and demand more content choices.

by Maury Wright, Editor in Chief

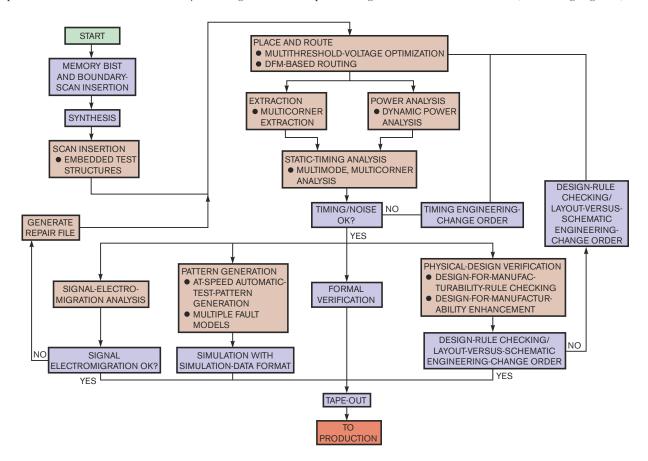

#### Is chip design different after 90 nm?

Design teams find that success requires some fundamental changes in thinking and in team structure in the 90- and 65-nm processes. by Ron Wilson, Executive Editor

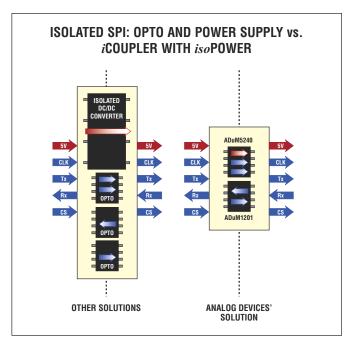

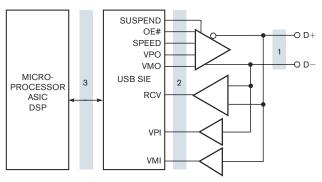

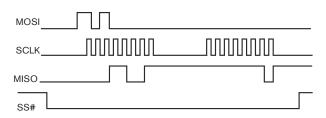

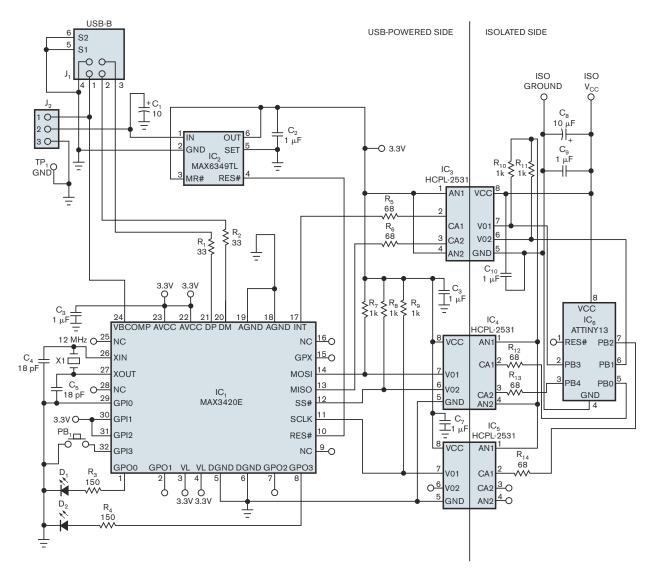

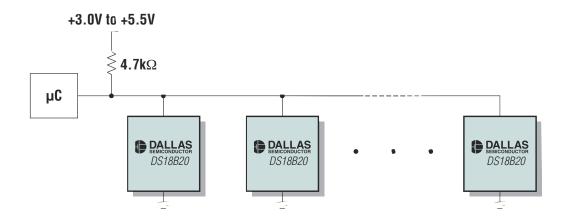

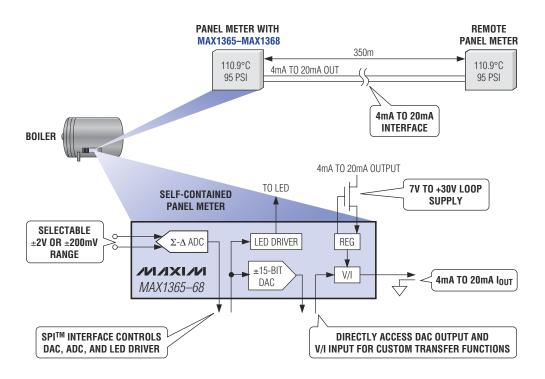

#### Isolating USB

With isolation, the USB fits a whole new crop of applications. by Lane Hauck, Maxim Integrated Products

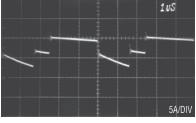

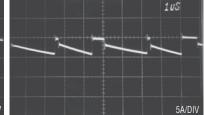

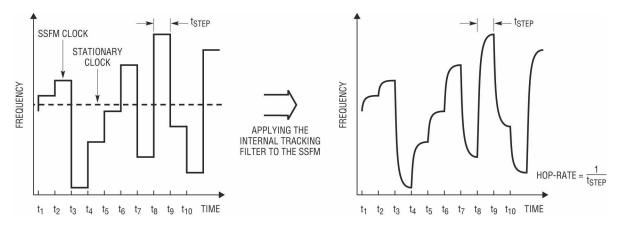

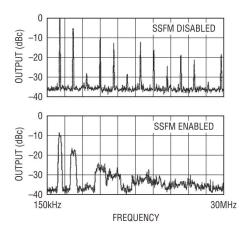

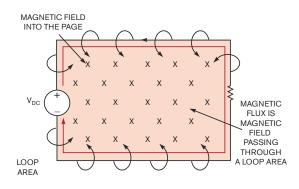

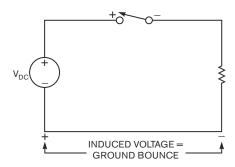

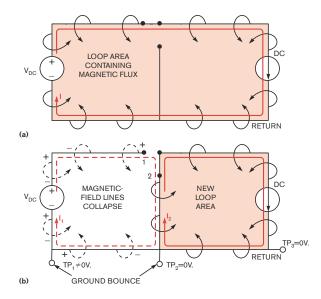

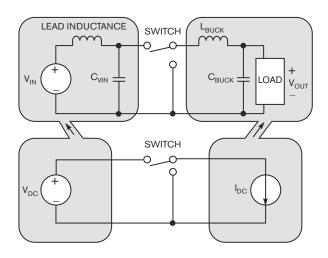

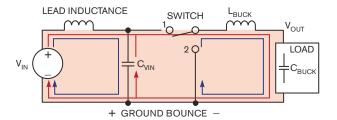

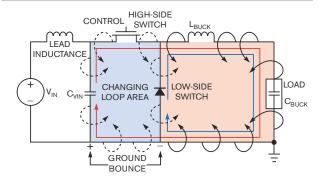

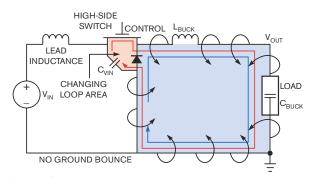

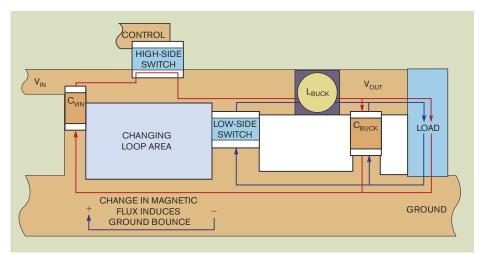

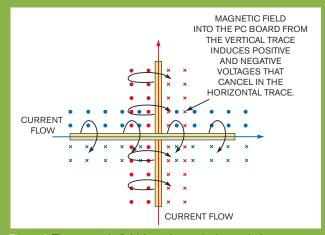

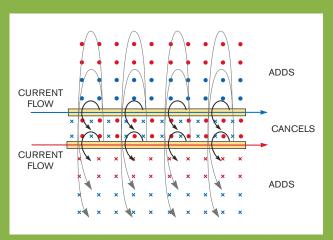

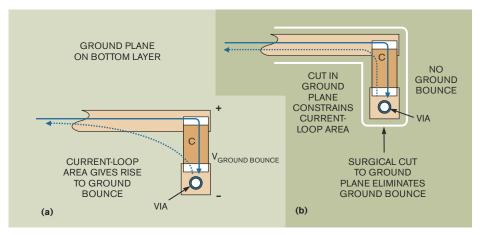

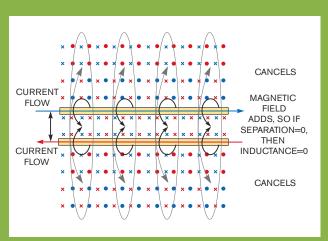

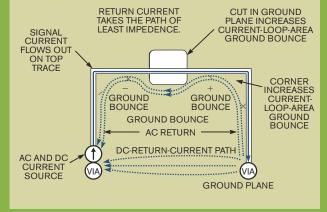

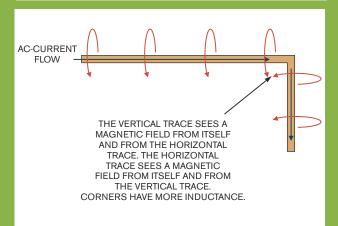

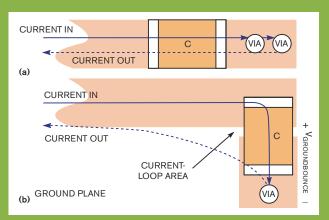

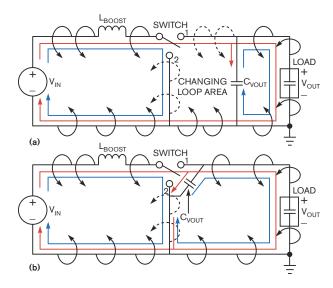

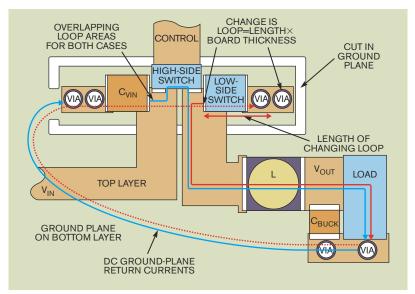

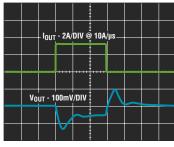

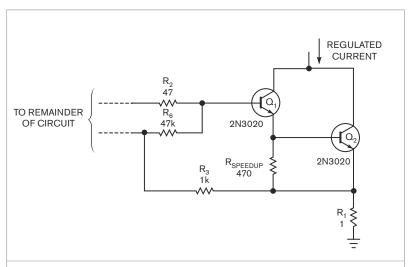

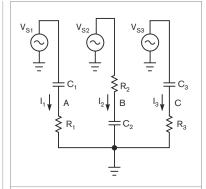

#### Reducing ground bounce in dc/dcconverter applications

Electrical ground, which looks simple on a schematic, can become complex depending on how you lay out the pc board. Unfortunately, ground-node analysis is difficult. However, understanding the physics of ground noise helps to reduce the problem.

by Jeff Barrow, Analog Devices

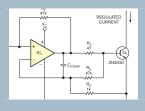

# DESIGNIDEAS

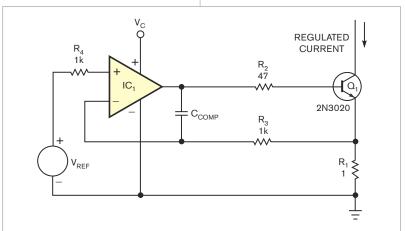

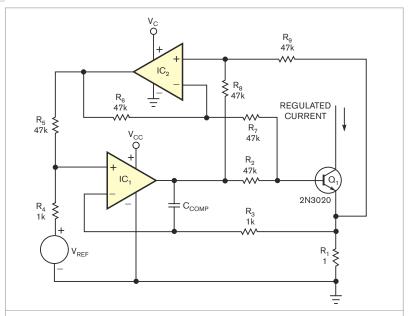

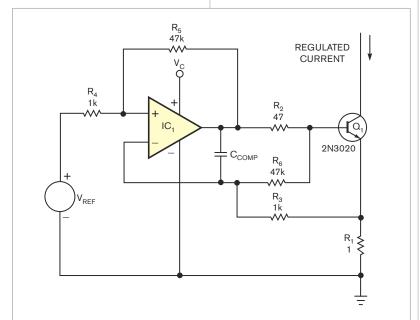

- 83 Error compensation improves bipolar-current sinks

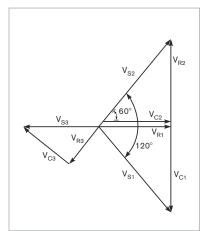

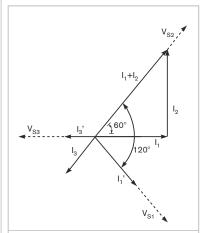

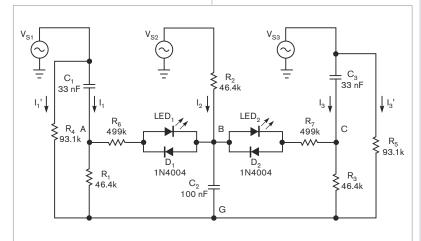

- 86 Phase-sequence indicator uses few passive components

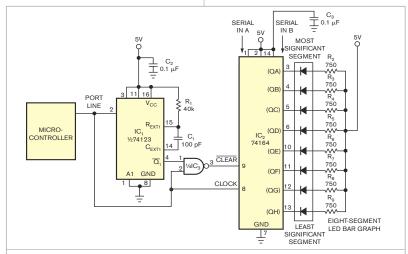

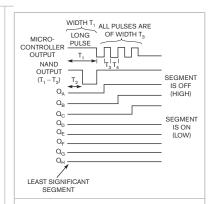

- 90 Microcontroller's single I/O-port line drives a bar-graph display

- Send your Design Ideas to EDNdesignideas@reedbusiness.com.

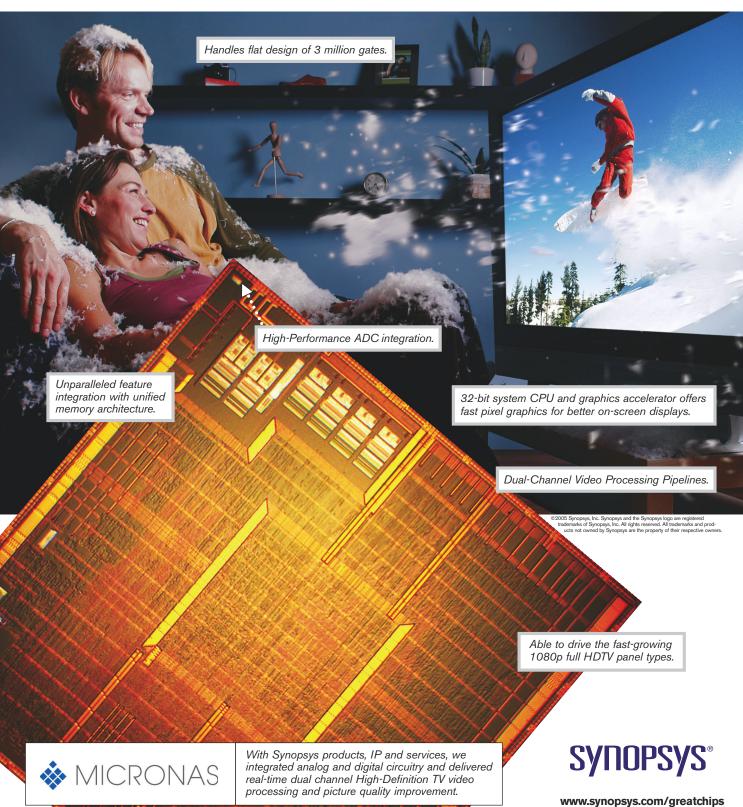

# "Redefining High Definition."

Ulrich Langenkamp / Project Manager VGC

### contents 7.6.06

- 23 Rugged wireless-sensor networks suit harsh industrial environments

- 23 Micron jumps into hybrid NANDs

- 24 C-synthesis tool adds features, capacity

- 26 Software optimizes networked-instrument usage

- 26 Toshiba spins 200-Gbyte, 2.5-in. hard-disk drive

- 28 Voices: Pat Gelsinger: Whither Intel?

- 30 Global Designer: Video op amps exceed HD needs; LEDs take over in "mood" lighting; I<sup>2</sup>C bus now runs at 1 MHz

93

## DEPARTMENTS & COLUMNS

- **EDN.comment:** Triple-play roadblocks: technology or competence?

- 32 Baker's Best: When is good enough good enough?

- 34 **Prying Eyes:** MP3 disassembly: tech for thrifty tune-toters

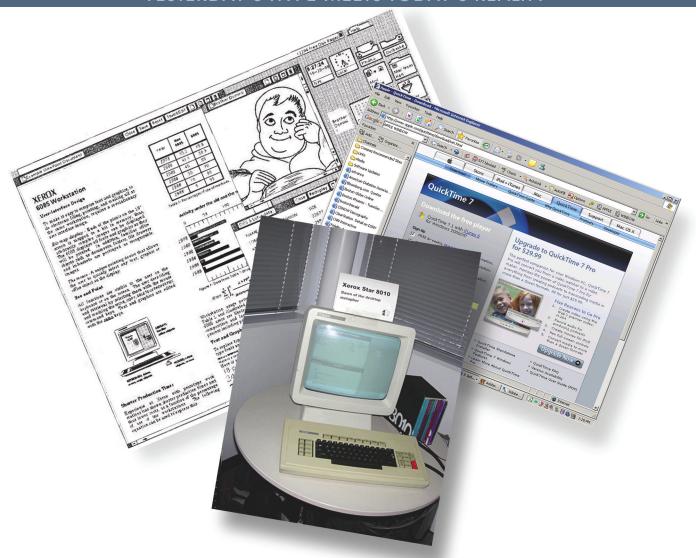

- 106 Reality Check: Xerox Star: The pioneer always gets the arrows

### PRODUCT ROUNDUP

- 93 Passives: Electrically programmable resistors, ceramic multianode chip capacitors, digitally programmable potentiometers, and more

- 94 Integrated Circuits: Radio-transmitter ICs, analog switches, RF synthesizers, power amplifiers, and more

- 97 Embedded Systems: Advanced TCA backplanes, CPUs, evaluation platforms, and more

EDN® (ISSN#0012-7515), (GST#123397457, R.B.I. Intl Pub Mail #0280844) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer, Stephen Moylan, President, Boston Division. Periodicals postage paid at Littleton, CO 80129-2345. Telephone (303, 410-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Ibn Blvd, Highlands Ranch, CO 80129-2345. Telephone (303, 410-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Ibn Blvd, Highlands Ranch, CO 80103-7500. EDN® copyright 2006 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$165 one year, Canada, \$226 one year, (includes 7% GST, GST#123397457); Mexico, \$215 one year; air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Mail Agreement No. 40685520. Return undeliverable Canadian addresses to: Deutsche Post, 4960-2 Walker Road, Windsor ON N9A 6J3. E-mail: subsmail@reedbusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 51, Number 14 (Printed in USA).

# Support Across The Board.

ACCELERATE TIME

SEEK TOTAL BOM SUPPORT

CONTROL PRODUCTION

COSTS

TO MARKET

Starting with in-depth design support all the way through to total supply chain management -Avnet Electronics Marketing is there for you. From concept to reality, we deliver:

Consultative engineering support and services

Focused product specialization

The broadest supplier partnerships in the industry

Over \$1 billion in top moving inventory "on the shelf"

World-class supply chain services

But, partnering with Avnet Electronics Marketing means much more than just having access to the industry's broadest array of design and supply chain services. It means working with a company that is truly focused on exceeding your needs and expectations - a company that is dedicated to giving you Support Across The Board.™

Ready. Set.

Enabling success from the center of technology

1 800 332 8638 www.em.avnet.com

WHEN DESIGN SUPPORT FOR CRITICAL SILVEDY CRITICAL

CALL AVNET ASAP!

# SIGNAL PATH designer®

Tips, tricks, and techniques from the analog signal-path experts

Feature Article....1-7

High Performance

Video Solutions.....2

HD-SDI Signal

Path Solutions ....4-5

Design Tools.....8

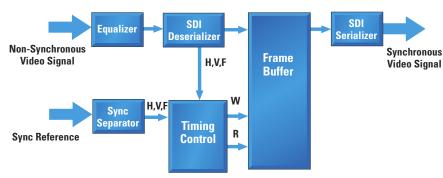

# Timing is Everything – The Broadcast Video Signal Path

— By Mark Sauerwald, Applications Engineer

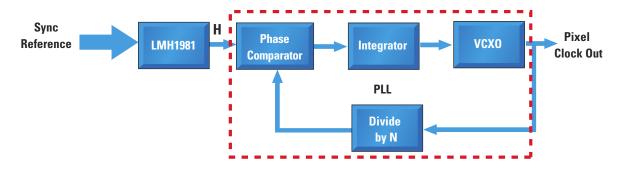

Figure 1. Major Components of a Genlock System

casual observer would note that there are many different broadcast video studios in the world, operating in different formats, some of them analog and some digital. There are multiple high definition television raster formats in use in the United States today. If you tried to count the number of different raster formats covered by the SMPTE292M HD standard, you would run out of fingers and toes. Within any studio there are many different signals, and they are all synchronized in lock step with one another. In video parlance, they are "genlocked."

Genlocking allows for easy switching from one signal to another (i.e., regular programming to commercials) without disrupting the synchronization circuits that are in the viewer's receiver. To do this requires that any signal coming from an outside source be genlocked to the rest of the signals in the studio. Most studios use an analog signal as their timing reference signal, and the timing information needs to be extracted from this signal to allow it to be used to genlock the incoming signal.

When a new signal is brought into a studio, whether it is coming from a satellite receiver, a camcorder, or any other source, the first thing to do is to synchronize it with the rest of the signals in the studio using a genlock circuit.

Figure 1 shows a block diagram for a genlock which takes an SDI (Serial Digital Interface) input signal, and synchronizes it with an analog reference

NEXT ISSUE:

Delay Calibration

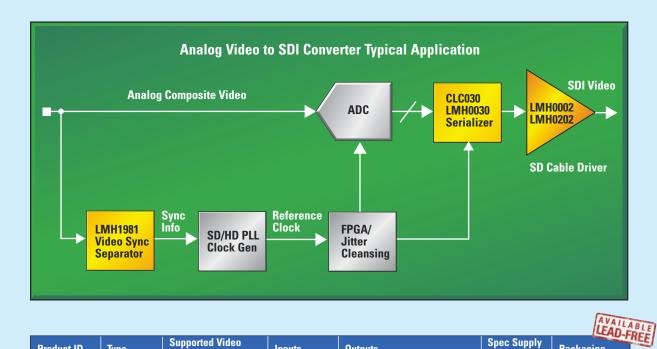

# **High Performance Analog Video Solutions**

|                | CEAD-F                         |                                                         |                |                                                                           |                          |               |  |  |  |  |

|----------------|--------------------------------|---------------------------------------------------------|----------------|---------------------------------------------------------------------------|--------------------------|---------------|--|--|--|--|

| Product ID     | Туре                           | Supported Video<br>Formats                              | Inputs         | Outputs                                                                   | Spec Supply<br>Range (V) | Packaging     |  |  |  |  |

| Sync Separator | s                              |                                                         |                |                                                                           |                          |               |  |  |  |  |

| LMH1981        | 50% slicing                    | NTSC, PAL, SECAM,<br>480i/p, 576i/p, 720p,<br>1080i/p   | 0.5 to 2.0 Vpp | H-sync, V-sync, odd/even,<br>burst/clamp, video format,<br>composite sync | 3.3 to 5                 | TSSOP-14      |  |  |  |  |

| LM1881         | 70 mV fixed                    | NTSC, PAL, SECAM                                        | 0.5 to 2.0 Vpp | V-sync, odd/even, burst/clamp, composite sync                             | 5 to 12                  | SOIC-8, DIP-8 |  |  |  |  |

| Video Converte | ers                            |                                                         |                |                                                                           |                          |               |  |  |  |  |

| LMH1251        | YPbPr to<br>RGBHV<br>converter | 480i/p, 576i/p 720p,<br>1080i, 1080p<br>XGA, SXGA, UXGA | YPbPr          | RGBHV                                                                     | 5                        | TSSOP-24      |  |  |  |  |

|                            |                |            |                      |                     |                         |                          | AVAILA<br>LEAD-F |  |  |  |

|----------------------------|----------------|------------|----------------------|---------------------|-------------------------|--------------------------|------------------|--|--|--|

| Product ID                 | Туре           | SSBW (MHz) | A <sub>V</sub> (V/V) | Slew Rate<br>(V/μs) | I <sub>CC</sub> (mA/Ch) | Spec Supply<br>Range (V) | Packaging        |  |  |  |

| Analog Crosspoint Switches |                |            |                      |                     |                         |                          |                  |  |  |  |

| LMH6582                    | 16 x 8         | 500        | 1                    | 3000                | 110 mA (total)          | ±3.3V to ±5V             | TQFP-64          |  |  |  |

| LMH6583                    | 16 x 8         | 500        | 2                    | 3000                | 110 mA (total)          | ±3.3V to ±5V             | TQFP-64          |  |  |  |

| Analog Multiple            | exers          |            |                      |                     |                         |                          |                  |  |  |  |

| LMH6570                    | 2:1 Mux        | 500        | 2                    | 2200                | 15                      | 6 to 12                  | SOIC-8           |  |  |  |

| LMH6572                    | Triple 2:1 Mux | 350        | 2                    | 1400                | 23                      | 6 to 12                  | SSOP-16          |  |  |  |

| LMH6574                    | 4:1 Mux        | 500        | 2                    | 2200                | 13                      | 6 to 12                  | SOIC-14          |  |  |  |

For more information on National's video amplifiers, visit www.national.com/see/videoamps

# SIGNAL PATH | designer

### **Broadcast Video Signal Path**

that is being supplied. In this edition of the Signal Path Designer, we will look at this application in detail, and examine the design considerations for each of the six blocks.

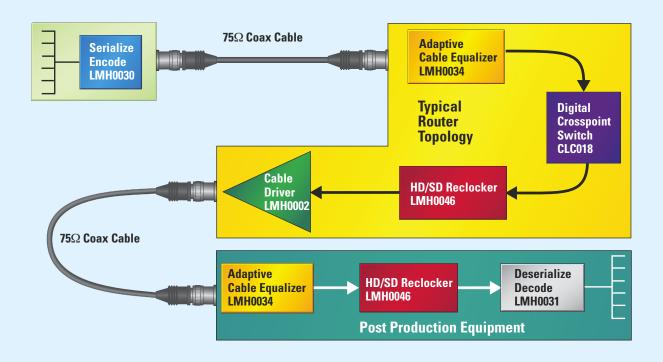

#### Cable Equalizer

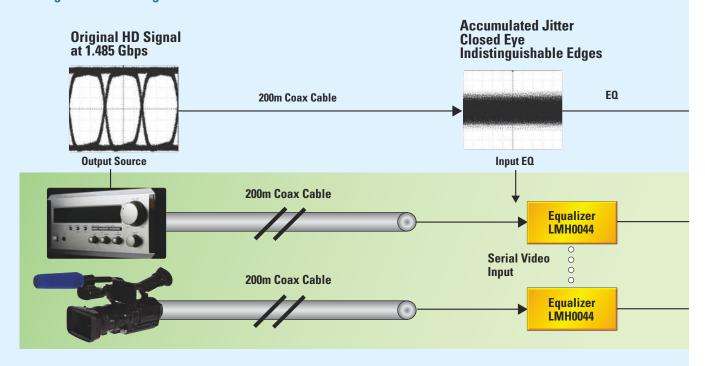

The SDI inputs on video broadcast equipment typically support long cable lengths: over 140m for high definition signals, and over 300m for standard definition signals. In order to support long cables, there needs to be a cable equalizer.

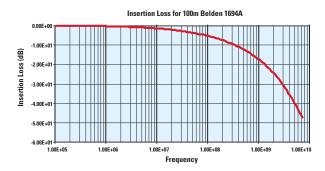

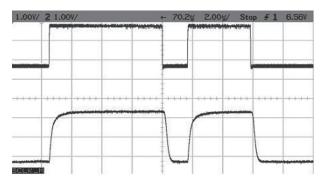

Long cables have a low-pass characteristic, where the attenuation of the input signal is proportional to the length of the cable, and the square root of the frequency. *Figure 2* shows the frequency response of a 100m length of a common (Belden 1694A) cable used in video installations.

Figure 2. Belden 1694A Frequency Response

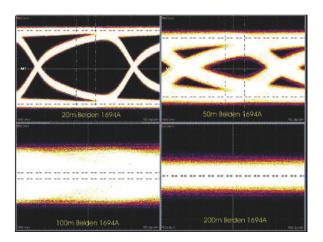

Although seeing the attenuation with frequency is helpful in designing the complementary filter that you will need to recover the signal, the image that you really want to see is the eye diagram. This tells you if there is there an opening big enough to recover the data. Figure 3 shows the eye diagrams for a 1.5 Gbps signal (an HD-SDI signal) after it has gone through various different lengths of cable. From the standpoint of this article, the primary result of the skin effect is that as the frequency increases, a smaller and smaller portion of the cross section of the cable will be carrying the signal, so there will be greater signal attenuation at higher frequencies than at lower frequencies. The response curve for this loss will be proportional to the  $\sqrt{\omega}$  which makes compensation difficult for standard types of filters.

Figure 3. Oscilloscope Traces of an HD-SDI Signal After Going Through Coax Cable

To attempt to match the frequency response of the cable, the designer carefully places the zeroes in his or her filter such that the resulting response is a close approximation to the  $\sqrt{\omega}$  response of the cable.

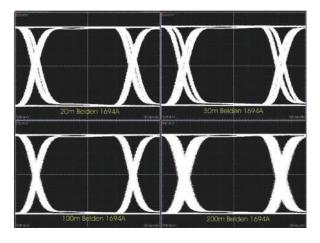

To deal with the fact that both high gain and high bandwidth are required at the same time, equalizer circuits are realized in exotic, high-speed processes such as the National's 0.25  $\mu m$  BiCMOS SiGe process. An example of one of these equalizers is the LMH0044 cable equalizer. With this part, you can recover signals at data rates of up to 1.5 Gbps through 200m of Belden 1694A cable.

Figure 4. Equalized Outputs

# **HDI-SDI Signal Path Solutions**

#### **SDI Signal Conditioning**

For more information, be sure to visit National's Broadcast Video Owners's Manual at www.national.com/see/bvom

|                       |                                                      |                     |                    |            |                                                                             | AVA               |

|-----------------------|------------------------------------------------------|---------------------|--------------------|------------|-----------------------------------------------------------------------------|-------------------|

|                       |                                                      |                     |                    |            |                                                                             | AVAILA<br>LEAD-FR |

| Product ID            | Function                                             | Max Speed<br>(Mbps) | Temp Range<br>(°C) | Eval Board | Comments                                                                    | Packaging         |

| Cable Drivers         |                                                      |                     |                    |            |                                                                             |                   |

| LMH0002MA             | HD/SD Serial cable driver                            | 1485                | -40 to 85          | SD002EVK   | Selectable slew rate                                                        | SOIC-8            |

| LMH0202MT             | Dual HD/SD Serial cable driver                       | 1485                | 0 to 70            | SD0202EVK  | Dual differential input,<br>dual differential output                        | TSSOP-16          |

| <b>Adaptive Equal</b> | izers                                                |                     |                    |            |                                                                             |                   |

| LMH0034MA             | HD/SD Adaptive cable equalizer                       | 143 to 1485         | 0 to 85            | SD0342EVK  | SMPTE 292M/259M<br>Serial recovery                                          | SOIC-16           |

| LMH0024MA             | 3.3V SD Adaptive cable equalizer                     | 143 to 540          | -40 to 85          | SD024EVK   | Footprint compatible with LMH0034                                           | SOIC-16           |

| LMH0044SQ             | HD/SD Adaptive cable equalizer                       | 1.485 Gbps          | 0 to 85            | SD044EVK   | Equalize up to 200m of cable at HD (1.485 Gbps)                             | LLP-16            |

| Encoder/Decod         | ers                                                  |                     |                    |            |                                                                             |                   |

| LMH0030VS             | SMPTE 292M/259M Digital video serializer/encoder     | 270 to 1485         | 0 to 70            | SD130EVK   | Integrated cable driver,<br>FIFO, BIST, and TPG                             | TQFP-64           |

| LMH0031VS             | SMPTE 292M/259M Digital video<br>serializer/ decoder | 270 to 1485         | 0 to 70            | SD131EVK   | FIFO, BIST, and TPG                                                         | TQFP-64           |

| Reclockers            |                                                      |                     |                    |            |                                                                             |                   |

| LMH0046MH             | HD/SD Reclocker                                      | 1.485 Gbps          | -40 to 85          | SD046EVK   | Dual differential outputs,<br>optional data rate clock;<br>27 MHz reference | TSSOP-20          |

# SIGNAL PATH | designer

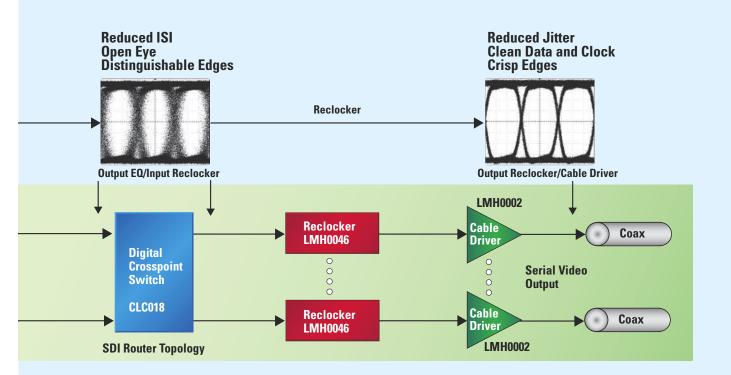

### **Broadcast Video Signal Path**

#### Deserializer

Once you have done the hard work of opening the eye of the signal coming in, you have to make sense of the bits that are coming at you, and this is the job of the deserializer. Video images have a very regular, repetitive format. They are composed of individual bits which are, at the next highest level of organization, divided into 10-bit words which are in turn divided into pixels. A series of pixels comprises a line, a series of lines makes up a field, and one or more fields are needed to complete the video frame. To sort out this organization, the SMPTE data sends a special sequence known as a Timing Reference Signal (TRS) at the start and end of each line. By detecting this TRS, it allows the receiver to figure out both the word and line alignment for the signal. At the end of each line, there are a couple of extra words inserted which tell the receiver what the line number is. A CRC is also included, so that the receiver will know if it has properly received all of the data in the line. There are a couple of things that can wreak havoc with receivers: DC content and long periods of time with no transitions. Most communications systems have a way to control this. In the case of the SMPTE 292 serial standard (HD-SDI) it is done with a combination of scrambling and encoding the data.

A good deserializer will extract all of this information for you, and present you with what you need. For this application, it consists of the picture data and the timing data. A deserializer such as the LMH0031 will do this for us, presenting the

picture data on two 10-bit data busses. The timing data is presented in the form of three digital signals representing H (start of a horizontal line), V (start of a vertical interval), and F (start of Frame). If the raster format is not interlaced, then you can use just H and V because they are the same.

The serial data is brought into the deserializer where it is decoded and descrambled. Then it is analyzed to find the TRSs which allows the deserializer to know how to break the bits into words. The TRSs' are further analyzed to extract the timing information which is encoded and the data is scrambled, it decodes and descrambles, then the framing is determined so that the deserialized data can be properly word aligned. All of this activity is generally done in the deserializer.

#### Sync Separator & PLL

Although the video world has gone mostly digital, one area where analog is still very common is in the sync-reference signal, which the studio uses to synchronize all of their equipment. The most common reference to use is a video signal which does not include picture information. This will consist of a series of pulses indicating the start of each video line, with a specific pattern that indicates the end of each field or frame. In this block of our genlock circuit, a sync separator circuit extracts H, V, and F (start of a horizontal line, start of a field, and start of a new frame) from the reference signal, and a PLL circuit generates a pixel clock which is synchronous with the reference signal.

Figure 5. Block Diagram of the LMH1981 Sync Separator & PLL Generating the Pixel Clock

For example, the LMH1981 is a high-performance multi-format sync separator that accepts standard analog SD or HD video signals with either bi-level or tri-level sync. It automatically detects the input video format and applies 50% sync slicing to ensure accurate sync extraction even if the input has irregular amplitude, offset, or noise conditions. To generate the pixel clock, a PLL should be set up to lock to the Hsync output of the LMH1981 and generate the desired clock frequency, which is typically 27 MHz for SD or about 74 MHz for HD. Something to consider when using a PLL for clock generation is that the divide ratio can be quite large and reduce loop bandwidth, which could make the PLL quite sensitive to jitter on Hsync. This makes it especially important to select a sync separator with a very low jitter Hsync output.

#### **Frame Buffer**

The frame buffer is simply a block of memory large enough to hold at least one entire frame of the image. This buffer needs to be dual port so that the data coming from the deserializer can be written into one side of the buffer, while data can be read from the other side of the buffer to be fed to the serializer. The buffer is organized in the same way as the video image, with consecutive pixels forming complete lines and consecutive lines forming the complete frame.

#### **Timing Control**

The timing control is the heart of the entire genlock system. The basic function is to control the writing into the frame buffer and the reading from the frame buffer. The timing control needs to keep track of two different timing domains. On the input side it receives the data, the timing information, and a clock from the deserializer. This data is written into the frame buffer, with a series of counters that keep track of the pixel and line information. This data is written synchronously with the clock being recovered from the deserializer. At the same time, the timing control takes the timing information coming from the sync separator and the pixel clock. These are used with a second set of counters to read data out of the frame buffer. This data is being read synchronously with the reference sync signal so that the image which was received by the deserializer is now being read synchronously with the reference. The data, along with the pixel clock are fed to the

serializer for output. Although video signals have very tight timing specifications, there will be some difference between the input and the output data rates, which means that eventually the frame buffer will either empty out, or overflow. The timing control circuitry has to recognize this situation and periodically repeat a frame or drop a frame to maintain the timing difference between input and output smaller than the size of the frame buffer.

#### Serializer

Once the data is read out of the frame buffer, it is in parallel format. Before it can be sent to the next piece of equipment it needs to be serialized and formatted to meet the SMPTE 292M HD-SDI standard. From a digital standpoint, new TRS characters are generated and inserted, new line numbers and CRCs are calculated and inserted, the data is then scrambled via the SMPTE scrambling algorithm and converted to NRZI format before being shifted out of a parallel to serial shift register. The key to doing all of this properly is to use a clock clean enough to meet the tight video timing specifications to shift the data out. SMPTE 292M allows no more than 0.2UI of jitter peak-to-peak on the serialized output, which means that the clock jitter needs to be below about 100 ps p-p. Most serializers take a clock which is at the parallel data rate as their input clock (for HD this would be approx 74 MHz) and then multiply it up to the serial rate of 1.5 GHz. Most good serializers will use a PLL for this multiplication that will reject some of the jitter in the original parallel clock. However, for the best performance it is best to start with the cleanest clock possible. In the example sync separator/clock generation circuit, you generated a pixel clock with a VCXO that has very low jitter so that added to the jitter rejection characteristics of the serializer will lead to a very low jitter output. Using the LMH0030 serializer with the VCXO clock source, you could expect your serial jitter to be approx 75 ps, well below the 0.2UI limit.

#### **Summary**

Using a handful of simple, off-the-shelf components, you can take a radical input video signal, which is marching to the beat of a different drummer, and get it to straighten up, and march with the rest of our signals. This way, you can switch from one program to another without disrupting the image on your screen.

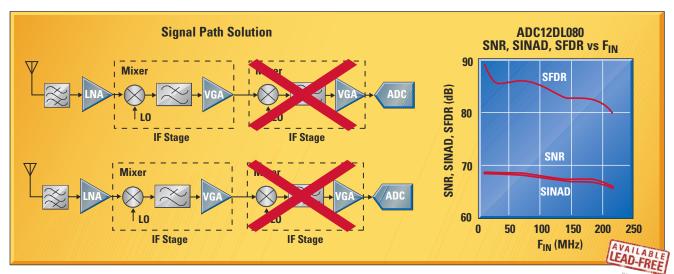

### **Design Tools**

#### **WEBENCH® Signal Path Designer® Tools**

Design, simulate, and optimize amplifier circuits in this FREE online design and prototyping environment allowing you to:

- Synthesize an anti-alias filter

- Select the best amplifier/ADC combo for your system specs

- Make trade-offs based on SNR, SFDR, supply voltage

- Simulate real-world operating conditions using SPICE

- Receive samples in 24 hours

webench.national.com

#### **WaveVision 4.0 Evaluation Board**

Test and evaluate A/D converters with National's easy-to use WaveVision 4.0 evaluation board. Each evaluation board comes complete with USB cable and support software.

#### **Features and benefits:**

- Plug-n-play ADC evaluation board

- USB interface to PC

- PC-based data capture

- Easy data capture and evaluation

- Highlighted harmonic and SFDR frequencies

- Easy waveform examination

- Produces and displays FFT plots

- Dynamic performance parameter readout with FFT

- Produces and displays histograms

#### **National Semiconductor**

2900 Semiconductor Drive PO Box 58090 Santa Clara, CA 95052 1 800 272 9959

Visit our website at: signalpath.national.com

For more information, send email to:

new.feedback@nsc.com

### Don't miss a single issue!

Subscribe now to receive email alerts when new issues of Signal Path Designer® are available:

signalpath.national.com/designer

Also, be sure to check out our Power Designer! View online today at: power.national.com/designer

# online contents

www.edn.com

Check out these online-exclusive articles: Ingredients: Miniature storage, embedded Wi-Fi, more

New chips and components for cooking up digital-consumer applications.

www.edn.com/article/CA6341326

### SID: Displays become more than dumb panels

With underlying technologies stabilizing, engineers must turn to system-level approaches for display improvements.

www.edn.com/article/CA6343832

#### Small displays present unique problems

The drive to put video, and eventually even high-definition video, on the small screens of portable products is creating a technological opportunity—or nightmare, if you prefer—of disproportionate size.

www.edn.com/article/CA6343860

#### Motion video blurs picture for big panels

The recent Society for Information Display Symposium in San Francisco painted a mixed picture for the large panels that dominate in the home-theater and television markets.

www.edn.com/article/CA6343858

#### TI lifts curtain on 45-nm process

Texas Instruments—always eager to let customers know early where it is going—used the forum of the Symposia on VLSI Technology to give an early look at its 45-nm process.

→ www.edn.com/article/CA6342037

#### **READERS' CHOICE**

A selection of recent articles receiving high traffic on www.edn.com.

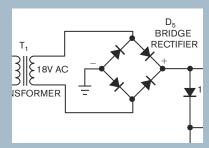

Design Idea: Obtain a lower dc voltage from a higher voltage power supply

www.edn.com/article/CA6339248

### Design Idea: Line-powered driver lights up high-power LEDs

www.edn.com/article/CA6339249

### EDA power-management standard: Spare us the drama, please

www.edn.com/article/CA6339253

### Toshiba spins 200-Gbyte, 2.5-in. hard-disk drive

www.edn.com/article/CA6340837

### Digital power lures system architects, power-supply vendors

www.edn.com/article/CA6335298

#### Displays invade embedded-system space

www.edn.com/article/CA6335299

### JFET-based dc/dc converter operates from 300-mV supply

> www.edn.com/article/CA6335301

## Don't pay for level translators in systems using multiple power-supply voltages

→ www.edn.com/article/CA6335309

### A simple software lowpass filter suits embedded-system applications

> www.edn.com/article/CA6335310

#### **NEW BLOGS**

EDN editors launch blogs devoted to power, EDA

#### **PowerSource**

Technical Editor Margery Conner tracks the latest developments in electronic power design and related technologies.

→ www.edn.com/powersource

#### Between The Lines

Senior Editor Mike Santarini offers insights on digital design and the EDA, ASIC, and FPGA industries.

www.edn.com/betweenthelines

#### See all of EDN's blogs

www.edn.com/blogs

#### **ARE YOU IMPATIENT?**

Use the following shortcuts to quickly reach the EDN content you want.

#### Design Ideas

→ www.edn.com/designideas

#### Prying Eyes

→ www.edn.com/pryingeyes

#### Tales From The Cube

→ www.edn.com/tales

#### Voices

→ www.edn.com/voices

#### Milestones That Mattered

→ www.edn.com/milestones

#### News and new products

→ www.edn.com/news

#### Technical features

→ www.edn.com/features

#### Columnists

→ www.edn.com/columnists

#### BY MAURY WRIGHT. EDITOR IN CHIEF

# Triple-play roadblocks: technology or competence?

had the pleasure of writing the cover story in this issue on next-generation broadband technology and how fast broadband links ultimately become the conduit for high-definition video into the home. The research and writing process was like a trip home, as I've followed the topic since the early '90s. Although the technology is fascinating and finally becoming affordable, recent real-life experiences make me wonder whether service providers are sufficiently competent to deliver an error-free triple play.

I first encountered the term "triple play"—delivery of voice, data, and video service over a converged network—around 1992 while doing public relations and technical writing for AT&T Microelectronics, the portion of AT&T that eventually became Agere (www.agere.com). AT&T's Bell Labs had developed both video-codec ICs that made compressed digital video a reality and technologies such as DSL (digital subscriber line) that might deliver such a stream. In fact, AT&T coined the term "switched-digital video" and described a vision close to those that VDSL2 (very-high-bit-rate-DSL) deployments realize today.

AT&T intended to deploy video-ondemand networks within a couple of years. Obviously, the technologists were overly optimistic. It would take more than five years before real DSL and cable deployments offered broadband-Internet-data services. And the triple play has become a reality just in the last few years.

But do the telecom companies and cable MSOs (multiple-service operators) have the competence and discipline to deliver? In North America, the telecom companies certainly understand how to build an ultrareliable network, but they are still struggling with how to compete in an open market and face suddenly unprofitable legacy networks. The MSOs have never really nailed customer service, and they are now offering must-work phone service.

I recently had a very trying experience with Cox Communications (www.cox.com). I have had cable-Internet service from Cox since the late '90s when the company first rolled out the network. DSL was not yet available in my neighborhood, and the cable service has been remarkably reliable since the day Cox installed it. But I've relied on DirecTV (www.directv.com) for video since 1996 when the company beat the MSOs to the punch with college-football pay-per-view pack-

Cox has peppered me with digital-TV offers, including HDTV and DVR. I finally decided to give the company a try, mainly because its HD-DVR offer was far cheaper than the one from DirecTV and it would offer the San Diego Padres in HD, as well.

The process went badly from the start. Cox entered data incorrectly in the computer, delaying installation. The company does not allow users to install the service themselves. When the technician arrived, his eyes glazed over when he looked at my video-distribution panel. I basically guided him step by step.

Well, the digital set-top box worked for about 10 minutes after the tech left. The tech also failed to remove the filter on the analog service to allow analog reception of an expanded channel set, although subscribing to that expanded service was a requirement for getting the digital service.

I called customer service, which told me that I had to schedule another appointment for the following week. I informed the service rep and a supervisor that Cox should fix the problem that day or just come pick up the equipment. They never called back or showed up.

I had been meaning to call Cox, but it wasn't an appealing thought, given the time on the phone that I knew it would require. Meanwhile, my bill arrived with nearly \$300 in charges for installation and services.

I just once again did my "phone-jail time" with a customer-service rep. She was nice enough to say that she would waive the service charges thus far. Of course, I informed her that I couldn't owe for something Cox never delivered. I've asked the company to remove the gear, but the rep insists that Cox must send a tech to verify my story before taking any action.

It seems that the triple-play competitors have the same disease afflicting mobile-phone carriers. They are quite adept at marketing and sales and nothing else. Here's hoping DirecTV stays focused on its core competence.EDN

Contact me at mgwright@edn.com.

#### MORE AT EDN.COM

+ Go to www.edn.com/ed1 and click on Feedback Loop to post a comment on this article.

# If you're doing POL or VRM, check out our SLC, MVR, MLC or SER.

SLC7530 0.05 - 0.4 μH Up to 50 A 6.7 x 7.5 mm 3 mm high

SLC7649 0.04 - 0.1 µH Up to 100 A 7.5 x 7.6 mm 5 mm high

SLC1049 0.08 - 0.15 µH Up to 61 A 6.9 x 10.2 mm

5 mm high

**MVRT** 0.25 -0.56 µH Up to 35 A 9.8 x 11.5 mm 5.1 mm high

0.36 - 2.3 µH Up to 36 A 9.8 x 11.5 mm 4.7- 7.8 mm high

MLC1200 0.36 - 4 μΗ Up to 37 A 10.5 x 11.2 mm

0.5 - 4.5 μH Up to 32 A 13.2 x 13.8 mm 4.1 - 6.1 mm high 3.9 - 6.5 mm high

SER1360 0.33 - 10 µH Up to 48 A 13.1 x 12.9 mm 5.8 mm high

SER1590 0.3 - 1 µH Up to 50 A 16.3 x 15.8 mm 10.2 mm high

SER2000 0.3 - 2 µH Up to 100 A 19.6 x 20.1 mm 8.6 - 14 mm high

# And get samples PDQ.

Only Coilcraft offers such a broad range of high current, low DCR power inductors.

They're perfect for Point of Load and Voltage Regulator applications. Or any place you need maximum current handling in minimum space.

Several models are rated up to 100 A rms. Others have powdered iron cores for maximum saturation current and minimum thermal aging.

Still others offer 5% DCR tolerance, making them ideal for current sensing applications.

As always, you can get free evaluation samples from our web site with just a click of the mouse. We ship same day!

Check out our full line of POL and VRM magnetics ASAP. Visit www.coilcraft.com/POL3

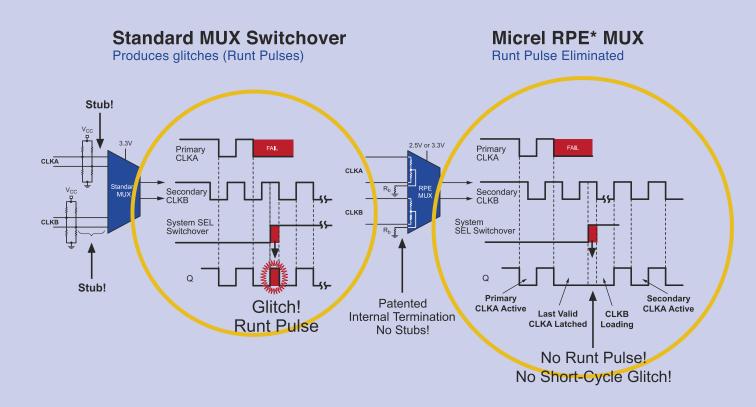

# New MUX Eliminates Short-Cycle Glitches in Clock Switchover Applications

First 1kHz to 1.5GHz non-PLL Multiplexer Family to Prevent "Runt Pulse"

#### **Choose the Ideal MUX for Your Precision, Low Jitter Clock Switchover Application**

| RPE MUX     | Description          | Any-Input<br>Interface | Output Logic    | Operating Frequency | Total Jitter         | Price <sup>1</sup> |

|-------------|----------------------|------------------------|-----------------|---------------------|----------------------|--------------------|

| SY89840/1/2 | 2:1 MUX              | Yes                    | LVPECL/LVDS/CML | 1kHz to 1.5GHz      | <10ps <sub>p-p</sub> | \$2.55             |

| SY89843/4/5 | 2:1 MUX w/1:2 Fanout | Yes                    | LVPCEL/LVDS/CML | 1kHz to 1.5GHz      | <10ps <sub>p-p</sub> | \$2.81             |

Note 1. 1,000 Piece Suggested Resale Price, FOB, USA

- ◆ No Runt Pulse Guaranteed!

- **♦** Fail-Safe Input No Oscillations When Input Fails

- ◆ Internal Termination No Stubs!

- ◆ Lowest Jitter MUX Isolation Minimizes Crosstalk

www.micrel.com

For more information, contact your local Micrel sales representative or visit us at: www.micrel.com/ad/sy8984x. Evaluation Board Requests and Applications Support: 1.408.955.1690 or hbwhelp@micrel.com.

<sup>\*</sup> Patent Pending. Runt Pulse Elimination (RPE)

#### PUBLISHER, EDN WORLDWIDE

#### John Schirmer

1-408-345-4402; fax: 1-408-345-4400; jschirmer@reedbusiness.com

#### **EDITOR IN CHIEF**

Maury Wright 1-858-748-6785; mgwright@edn.com

#### EXECUTIVE EDITOR

Ron Wilson 1-408-345-4427; ronald.wilson@reedbusiness.com

#### MANAGING EDITOR

Kasey Clark 1-781-734-8436; fax: 1-781-290-3436; kase@reedbusiness.com

#### EXECUTIVE EDITOR, ONLINE Matthew Miller

1-781-734-8446; fax: 1-781-290-3446; mdmiller@reedbusiness.com

#### SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-781-290-3307; moleary@reedbusiness.com

#### EMBEDDED SYSTEMS

Warren Webb, Technical Editor; 1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com

#### ANALOG

Paul Rako, Technical Editor; 1-408-745-1994; paul.rako@reedbusiness.com

#### EDA. MEMORY.

#### PROGRAMMABLE LOGIC

Michael Santarini, Senior Editor; 1-408-345-4424; michael.santarini@reedbusiness.com

#### MICROPROCESSORS, DSPs, TOOLS

Robert Cravotta, Technical Editor; 1-661-296-5096; fax: 1-781-734-8070; rcravotta@edn.com

#### MASS STORAGE, MULTIMEDIA.

PCs AND PERIPHERALS Brian Dipert, Senior Technical Editor; 1-916-760-0159; fax: 1-781-734-8038;

#### bdipert@edn.com POWER SOURCES,

#### ONLINE INITIATIVES

Margery Conner, Technical Editor; 1-805-461-8242; fax: 1-805-461-9640; mconner@connerbase.com

#### DESIGN IDEAS EDITOR

Brad Thompson edndesignideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR Frances T Granville, 1-781-734-8439;

rances I Granville, 1-781-734-843 fax: 1-781-290-3439; f.granville@reedbusiness.com

#### ASSOCIATE EDITOR

Maura Hadro Butler, 1-908-347-9605; mbutler@reedbusiness.com

#### EDITORIAL/WEB PRODUCTION MANAGER

Diane Malone, Manager

1-781-734-8445; fax: 1-781-290-3445

Steve Mahoney, Production/Editorial Coordinator

1-781-734-8442; fax: 1-781-290-3442

Melissa Annand, Newsletter/Editorial Coordinator

Contact for contributed technical articles

1-781-734-8443; fax: 1-781-290-3443

Adam Oddordi, Prepress Manager

1-781-734-8325; fax: 1-781-290-3325

#### CONTRIBUTING TECHNICAL EDITOR

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson, PhD; Bonnie Baker; Joshua Israelsohn

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Brashears, Production Manager 1-781-734-8328; fax: 1-781-734-8086 Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-781-734-8086 Pam Boord, Advertising Art 1-781-734-8313; fax: 1-781-290-3313

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SMZ 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

#### EDN ASIA

Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirlimaya Varma, Editor in Chief kirli.varma@rbi-asia.com

#### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Kenji Tsuda, Editorial Director and Editor in Chief tsuda@reedbusiness.jp Takatsuna Mamoto, Deputy Editor in Chief t.mamoto@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

#### DENNIS BROPHY

Director of Business Development Mentor Graphics

#### DANIS CARTER

Principal Engineer, Tyco Healthcare

#### CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne

DMITRII LOUKIANOV

#### System Architect, Intel

RON MANCINI

#### Engineer

GABRIEL PATULEA

#### Design Engineer, Cisco

MIHIR RAVEL

VP Technology, National Instruments

#### DAVE ROBERTSON

Product Line Director, Analog Devices

#### SCOTT SMYERS

VP Network and System Architecture Division, Sony

#### TOM SZOLYGA

Program Manager, Hewlett-Packard

#### JIM WILLIAMS

Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000; fax: 1-781-734-8070. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

# Simple. Complete. USB Data Acquisition.

# **NI CompactDAQ**

NI CompactDAQ provides the plug-and-play simplicity of USB for sensor, electrical, mechanical, and physical measurements. It delivers fast and accurate data acquisition in a small, simple, and affordable system.

- Hi-Speed USB (2.0) for up to 3.2 MS/s signal streaming

- Multiple connectivity options for sensors and signals

- Hot-swappable modules with built-in signal conditioning

- Simple setup with hardware autodetection

- Driver for National Instruments LabVIEW and text- based languages included

Take a virtual tour of NI CompactDAQ at ni.com/compactdaq.

800 327 9894

© 2006 National Instruments Corporation. All rights reserved. LabVIEW, National Instruments, NI, ni.com, and NI CompactDAQ are trademarks of National Instruments. Other product and company names listed are trademarks or trade names of their respective companies. 2006-6881:301-101-D

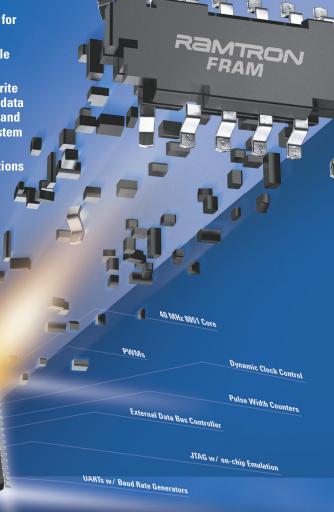

# Announcing the FRAM-Enhanced 8051 MCU

The first microcontroller with integrated nonvolatile FRAM

#### A Breakthrough Combination

The VRS51L3074 combines a high performance microcontroller with nonvolatile FRAM memory for the ideal data acquisition solution.

Ramtron integrates FRAM into its fast and flexible Versa 8051s, simplifying the design cycle:

Say goodbye to limited endurance, drawn out write cycles and code overhead accompanying Flash data storage. Use FRAM memory instead, for a quick and reliable nonvolatile data storage/processing system that only a FRAM enhanced MCU can provide.

The VRS51L3074 targets a wide array of applications from sensors and metering to industrial control, instrumentation and medical devices.

12C

On-Board Oscillator

Find out how Ramtron can raise the standard of your next design by calling 1-800-943-4625 x 208 or simply email mcuinfo@ramtron.com

#### **High performance MCU:**

- 40-MIPS, single-cycle 8051 core

- 40 MHz precision internal oscillator

- MAC and Div unit for DSP operations

- 64KB ISP/IAP Flash, 4KB SRAM

- Robust set of enhanced, highly configurable digital peripherals

#### **8K Bytes FRAM:**

- No Delay writes

- Unlimited read/write endurance

- True nonvolatile RAM (no battery required)

- . No algorithms or protocols to write data

- Byte-addressable writes

www.ramtron.com

# Rugged wireless-sensor networks suit harsh industrial environments

Industrial environments are usually harsh, with hazards such as strong mechanical vibrations, high temperatures, noisy electrical environments, and even explosive gases. It's difficult and expensive to install wiring in these situations, which range from oil rigs to refineries. Thus, these applications are primary targets for ultralow-power wireless-sensor networks.

The M1030, an embedded node for the SmartMesh-XT wireless-sensor network, suits harsh industrial environments.

Targeting this market, Dust Networks has released SmartMesh-XT, an enhancement of its mesh-networking platform. The system offers a rugged design for Class 1 Division 1 environments, including vibration resistance and an industrial-temperature range of -40 to  $+85^{\circ}$ C. The company claims that the network, which relies on the company's TSMP (Time Synchronized Mesh Protocol), achieves

reliability greater than 99% in such electrically noisy environments. TSMP, a media-access and networking protocol, operates on standard, off-the-shelf radio chips and allows every node in the mesh network to act as a router.

This product targets use in applications employing the HART (Highway Addressable Remote Transducer) Protocol, which the HART Communication Foundation supports. The protocol, an industrial standard for device communication, calibration, and maintenance, comprises a 4- to 20-mA analog line and a digital signal on the analog line. Rob Conant, Dust's co-founder and vice president of marketing, says, "Most HART devices today don't enable the digital-calibration data because you have to superimpose the digital data on the analog line and go through the distributed-control system." He claims that, by using a separate wireless network to handle the digital diagnostic and calibration data, HART enables you to handle data in parallel rather than intermingling with mission-critical control signals. He says that 25 million HART devices are in use and that most don't enable digital-calibration data.

The family of products comprises network nodes and managers in both the 900-MHz and the 2.4-GHz bands. The 900-MHz products include the M1030 "mote," or node, and the PM1230 embedded-system manager. The 2.4-GHz products, which use IEEE 802.15.4 radios, include the M2135 mote and the PM2130 embedded-system manager. The communication distances for the networks range from 75 to 300m.—by Margery Conner

Dust Networks, www.dustnetworks.com.

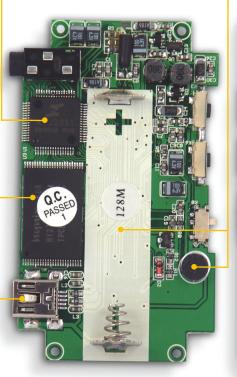

# Micron jumps into hybrid NANDs

With hybrid-NAND pioneers Samsung (www.samsung.com) and M-Systems (www.m-systems.com) feuding, Micron Technology is seizing the opportunity to introduce a hybrid-NAND device targeting the high-end-cell-phone market. M-Systems and Samsung offer the MDOC (disk on chip) and OneNAND, respectively, which allow designers to boot cell phones using a NAND-based device. Doing so eliminates the need for a NOR device and the extra chip that device involves and adds the capacity and write-speed advantage of NAND. Micron calls its offering the Managed NAND. Like MDOC, Managed NAND pairs a flash die with a microcontroller on a single MCM (multichip module), allowing the company to swap out NAND as higher density NAND becomes available. In contrast, Samsung's monolithic OneNAND device is an SOC (system on chip).

Bob Leibowitz, Micron's NAND-product-marketing director, claims that the Managed NAND is easier to design into wireless handsets than are competing products. He says that, whereas legacy hybrid devices require a design-in, using Managed NAND is akin to qualifying a hard drive for your design because MCM connects to the MMC (multimedia-card) port on wireless processors. The Managed NAND devices have data-transfer rates as high as 52 Mbytes/sec and come in voltages of 1.8V with 1.8V I/O or 3.3V with 3.3 or 1.8V I/O in single-levelor multilevel-cell technology. The product is currently available for sampling and should enter mass production in 2007.

-by Michael Santarini

▶Micron Technology, www.micron.com.

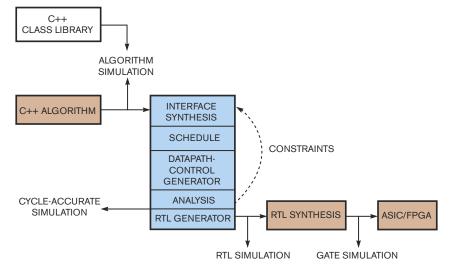

# C-synthesis tool adds features, capacity

entor Graphics has introduced a higher capacity version of its Catapult C ANSI-C++-based synthesis tool that designers can now use to build a prototype of a full DSP-based subsystem. Mentor in 2004 introduced the first version of its Catapult C tool to help IC architects design DSP-centric SOC (system-on-chip) blocks at an algorithmic level. Unlike other ESL (electronic-systemlevel)-design tools that run on specialized languages, the Catapult C tool uses ANSI-C++ as an input and generates RTL (register-transferlevel) design for hardware design, as well as a SystemC transaction-level model for simulation.

"The source description is strictly functional," says Shawn McCloud, Catapult's product-marketing manager. The source description requires no hardware detail, he claims. Instead, the synthesis tool inserts the hardware detail. "This separation of technological intent from functional specification is a key driver of the technology," says McCloud.

Since its formal introduction in 2004, Catapult C has seen the highest adoption rate of any Mentor tool, he claims, growing 145% in 2005 over

2004. It has seen its highest adoption in Japan. That version of the tool suited only block-level synthesis. The new version of the tool, Catapult SL (system level) adds support for hierarchy and other features that allow architects to use the tool to design a subsystem prototype. The company added a new hierarchical engine that increases the tool's capacity and manages complexity. "Like any other tool in this area, the older version of Catapult synthesized individual blocks. Users would then have to stitch the blocks together," says McCloud. Catapult SL can now do multilevel subsystems.

McCloud says that customers have used the SL tool to design 3.5 million-gate sub-

systems. However, the company believes that the tool can handle 10 million or more gates. The algorithm performs a top-level analysis, propagates all that information to the lower level blocks, and then independently optimizes each block. The tool can reorganize sequential functions to make them run concurrently. A new channel-synthesis feature optimizes the interfaces between the blocks in the subsystem. "It automatically does the analysis of the data rates between the blocks and then automatically inserts the appropriate channel size, FIFO depth, or memory depth to prevent the system from locking when you pipeline the subsystem," McCloud says. Thus, channel synthesis coordinates the communications between the blocks.

The tool can also automatically implement carry-save-adder trees in one step and can generate a SystemC TLM (transaction-level model) that you can feed into Mentor's Questa multilanguage simulator. That tool can generate VCD (value-change-dump) files that you can feed into third-party power tools and then return to Catapult SL to analyze power consumption.

With the introduction of Catapult SL, Mentor has changed the naming convention of its entire Catapult lineup. The original version of Catapult C++ is now Catapult BL (block level) and costs \$140,000 for an annual license. The company also offers the ANSI C++ Catapult LB (library builder). Catapult SL costs \$350,000 for an annual subscription.

#### —by Michael Santarini ▶Mentor Graphics,

www.mentor.com.

You can use the Catapult SL tool to design DSP-centric SOC blocks.

#### **DILBERT** By Scott Adams

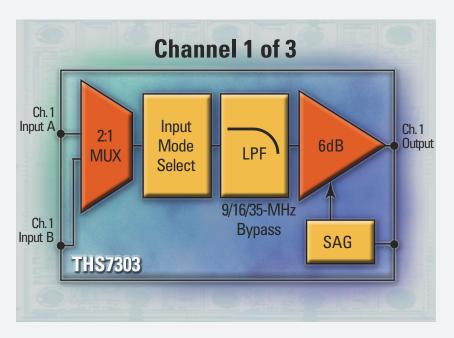

# 3-Ch. Low-Power Video Amp with I<sup>2</sup>C Control

The **THS73x3** family of high-performance video amplifiers from Texas Instruments provides the designer with unprecedented flexibility and control in configuring video systems without the need for hardware upgrades or modifications. Operating at 20x less power than competing amplifiers, these products are ideally suited for digital video systems like those incorporating TI's DaVinci™ and DLP® technologies.

| Device  | # of<br>Channels | Filter -3 dB<br>Freq<br>(MHz) (typ) | Filter | Bypass<br>Bandwidth<br>(MHz) (typ) | Gain<br>(dB)     | Input<br>Coupling                   | Output<br>Coupling | SAG<br>Output | Price<br>Starts<br>at 1K |

|---------|------------------|-------------------------------------|--------|------------------------------------|------------------|-------------------------------------|--------------------|---------------|--------------------------|

| THS7303 | 3                | 9, 16, 35                           | 5      | 190                                | 6                | AC-Bias,<br>AC-STC,<br>DC, DC+Shift | AC or DC           | Yes           | \$1.65                   |

| THS7313 | 3                | 8                                   | 5      | -                                  | 6                | AC-Bias,<br>AC-STC,<br>DC, DC+Shift | AC or DC           | Yes           | \$1.20                   |

| THS7353 | 3                | 9, 16, 35                           | 5      | 150                                | 0,<br>Adjustable | AC-Bias,<br>AC-STC,<br>DC, DC+Shift | AC or DC           | No            | \$1.65                   |

#### **▶** Applications

- Set-top boxes

- Digital televisions

- Personal video/DVD recorders

- Portable USB devices

#### **▶** Features

- 2.7V to 5V single-supply operation

- Low power consumption: 55mW at 3.3V

- 2:1 Input MUX allows multiple input sources

- I<sup>2</sup>C Control of all functions

- Integrated low-pass filters with 5th-order Butterworth characteristics

- Selectable input coupling modes

- Rail-to-rail outputs allow a variety of AC- or DC-coupled modes

- Individual channel disable with independent channel mute control

For Samples,

Evaluation Modules and

Technical Information

www.ti.com/ths7303 o 800.477.8924, ext. 13277

DaVinci, DLP, Technology for Innovators and the red/black banner are trademarks of Texas Instruments. 1566A0

© 2006 TI

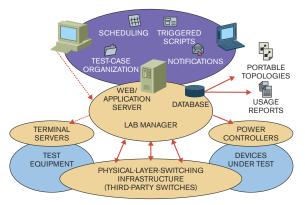

# Software optimizes networked-instrument usage

denTree Technologies has announced Lab Manager 5.0, a re-engineered version of its awardwinning network-lab-automation software. The Lab Manager open-lab operating system works with any kind of network equipment, managing the physical-layer infrastructure to which test equipment and devices under test connect. The result is a softwarecontrolled lab environment with a drag-and-drop user interface that allows engineers to easily and remotely design and implement topologies. The software schedules topologies, configurations, and test scripts; searches for available devices; and reports on device usage. Because it supports a wide range of switches, Lab Manager works in any lab with any devices and any interface types, including POTS (plainold telephone service)/analog, any rate of Ethernet, optical, Fibre Channel, and RF/coaxial interfaces.

A key reason that labs use the package is to share expensive test equipment among multiple users and multiple test beds. The queue-based scheduler enhances this capability by queuing tests to run as soon as equipment becomes available. Administrators can adjust the priorities or insert higher priority projects into the queue. Another new feature is integration with power con-

trollers, allowing test engineers to control power cycling and system rebooting directly from the GUI. In addition, test engineers can write scripts to control test topologies. Flexible user- and group-level-access permissions allow customers and partners to partic-

ipate in testing and enable the lab to control its test beds.

Users typically implement Lab Manager 5.0 with their switching infrastructure; list price is \$100 per managed port.—by Dan Strassberg EdenTree Technologies, www.edentreetech.com.

Lab Manager 5.0 coordinates, automates, and simplifies the scheduling of virtually any type of networked lab resources.

# Toshiba spins 200-Gbyte, 2.5-in. hard-disk drive

As digital video continues to expand in scope and volume, consumers continue to pile up large data files that-like those dust-gathering VHS settes-they are unwilling to delete. Without a viable backup medium for such data volumes, the demand for hard-diskdrive-storage capacity continues to climb for any category of device that is likely to have video on it. Consequently, portable media players and notebook computers are beginning to drive the areal-density curve in the hard-drive market.

The move started with the Apple (www.apple.com) Video iPod and similar devices. Physical constraints dictated a 1- or 1.8-in., low-profile hard-disk drive, but storage demands quickly exceeded the capabilities of conventional lateral recording. The drive industry's

next big idea, PMR (perpendicular magnetic recording), began to first appear in tiny drives. For example, Toshiba's storage-device division introduced PMR to its product line in a 1.8-in. drive for media players. The advantage of PMR is its ability to record with the magnetic lines of flux entering the medium vertically rather than laterally across its surface, providing the same volume of magnetic dipoles in a smaller surface area. Hence, the technology provides higher potential areal density for the same SNR. Manufacturers still need to address increasing the recording-signal frequency or slowing the platter to get more bits per millimeter along the track, and moving the tracks closer together.

To get the magnetic-flux lines vertical, Toshiba designed a tunnel-magnetoresistive recording head. Combining all these technologies-PMR, greater bit frequency and track density, and the new head technology-the company recently announced a 200-Gbyte, dual-platter, 2.5-in. drive. The drive targets high-end notebook applications for serious gamers, video junkies, and packrats. Samples are in qualification at high-end-notebook vendors, and Toshiba expects to begin production shipment in August.

This move will not be a oneshot technological leap, according to the company. Theoretically, the limit on achievable areal density for PMR is approximately 1 Tbit/in.², compared with the roughly 180 Gbits/in.² on the new drive. Toshiba expects for some time to continue driving media, head design, signal paths, and positioners. So, although terabit density is not imminent, Toshiba could drive the current technology platform to produce 500 Gbytes or more in the 2.5-in. form factor.

—by Ron Wilson ▶Toshiba, www.toshiba.com.

#### FROM THE VAULT

"'Smaller than a breadbox, 4k words of memory, and less than \$10,000.' Remember when that was the definition of a minicomputer? Nowadays, it's not so easy! Today's mini is yesterday's mainframe, and tomorrow's is likely to be today's microcomputer."

Robert Grossman, Senior Editor, and John Conway, Associate Editor, *EDN*, June 5, 1976

# Easy.

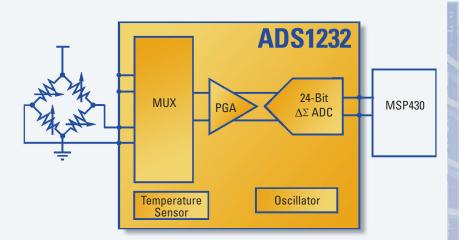

#### **World's Lowest Power MCU**

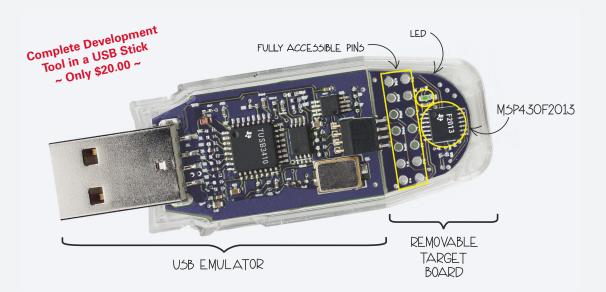

It's easy to rev up your application in minutes with the new **eZ430-F2013**, the world's smallest complete development tool for only **\$20!** The tool provides all hardware and software needed to evaluate the MSP430 or complete an entire F20xx project. The F20xx combines 16 MIPS performance, less than 1 microamp standby current, with your choice of analog converters - from a comparator, fast 10-bit ADC to 16-bit sigma-delta with integrated PGA- all in a package as tiny as 4x4 mm. **Designing with the world's lowest power MCU just got even easier.**

#### **New Low Pin-Count Devices**

| Device      | Program | SRAM  | SPI, I <sup>2</sup> C | Analog     | Price 1K USD |

|-------------|---------|-------|-----------------------|------------|--------------|

| MSP430F2001 | 1 KB    | 128 B | _                     | Comparator | \$0.55       |

| MSP430F2011 | 2 KB    | 128 B | _                     | Comparator | \$0.70       |

| MSP430F2002 | 1 KB    | 128 B | $\checkmark$          | 10-bit ADC | \$0.99       |

| MSP430F2012 | 2 KB    | 128 B | $\checkmark$          | 10-bit ADC | \$1.15       |

| MSP430F2003 | 1 KB    | 128 B | $\checkmark$          | 16-bit ADC | \$1.50       |

| MSP430F2013 | 2 KB    | 128 B | <b>√</b>              | 16-bit ADC | \$1.65       |

Order Today! www.ti.com/ez430 o 800.477.8924, ext. 1313

# **VOICES**

#### Pat Gelsinger Whither Intel?

at Gelsinger, senior vice president and general manager of Intel's Digital Enterprise Group, recently talked about Intel's future directions, how the company will build on its core competencies, and new processors and who will benefit from them. Excerpts of that interview follow, and you can find the full interview at www.reed-electronics. com/electronicnews/article/CA6329160.

#### Is innovation leveling off, or is it increasing?

In some ways, you're seeing clear trends toward less innovation at the chip level because of the cost. What does a 65-nm chip cost? That's why we've seen the number of ASICs declining. At the same time, you're seeing things like FPGAs growing. You take all that together, and there are fewer silicon designs than there were in the past. As we make these architectural transitions to a quad- or eight-core and multicore architectures, we're seeing an acceleration of innovation. I think we were in a period that was boring for a number of years. I see them getting exciting in the future.

It also looks as if other pieces have come a long way, too, so that the integration of all of these technologies can make a much more innovative device.

I'd agree with that. Innovation is a nonlinear activity. It's not as if Moore's Law is just plunking along and innovation is moving with it. You get to points in which dislocations happen. When Windows happened, it wasn't just as if one day you couldn't do it and then the next day you could. All of a sudden, you had enough excess capacity to change the paradigm of the user interface. We have reached a period in which there's enough excess capacity that you're seeing that next step of innovation. General connectivity is in place across a broad wireless system. There are thin and light form factors. You can start putting a lot of functions into small form factors, and enough computing capacity is left over for your application to become interesting. I do see a cross with high-density memory's changing the memory hierarchy. On the horizon, there are major changes in what we consider a computing device.

Something else seems to have changed here, as well. Intel used to be far more independent. It now seems to be more reliant on a ring of partnerships.

In many ways, I see that as a skill we've developed. We couldn't do USB. We had to use third-party silicon, we had to facilitate plugfests, and we had to enable the usage-model branding in the industry. We did it with PCI, and we did it with AGPs [accelerated graphics ports]. It's not a new skill, but the scope and the breadth have changed, be-

cause now we're trying to facilitate an entire service relationship through broader ecosystem players across global environments. Wi-Fi was a baby step for some of the things we're trying to do now.

#### Has Intel's core competency changed?

Some elements of our A core competency are unending: underlying process technology; the ability to manufacture in high volume; and sophisticated, high-volume design. That's what we do. Some of these other competencieswe now have thousands of software engineers engaging with service providers, being able to facilitate end-user models-these are things we layer on top of those core competencies. It's pretty far from where we were a decade ago.

#### Intel is experimenting in a lot of other areas, such as life sciences, too. Where is Intel going with that?

Our health-care activities fall into three areas. One is IT in institutional health care. How do you accelerate adoption of that? My PC is a lousy form factor when you think of doctors and nurses trying to handle their activities. That's traditional IT in institutional health care. IT penetration in health care around the world is the lowest of any of the major verticals. That is a frightening statement. The second area is personal health care. We have mainframe health care, called hospitals. Now we need the PC version, or personal health care, with connection into the home environment and into self-care.

#### What's the third area?

The things we build at the transistor level are now smaller than all of the components that are the basis of life-proteins, genes, DNA. We can start analyzing at the single-DNA level. This is the deep biological science. We have the world's greatest chemists and physicists and the finest analytical tools on the planet. We added a few biologists, and we're getting great results. We can do a single-DNA analysis or a singleprotein analysis. We can detect protein deviations that no one has analyzed before.

#### But each core is still a processor that deals with ad hoc queries. Haven't those always been a nightmare for multiprocessing systems?

Yes, and, as a result, we're spending a lot of time looking at workloads, so we can take advantage of those. If everything's a single stream of execution leading to another single stream leading to another, you don't gain a lot of parallelism. Those types of applications are not going to see enormous leaps in capability. At the same time, most of those applications don't need a whole lot of performance. New applications, such as recognition and human interface, mining, and synthesis, have enormous potential for parallelism.

-by Ed Sperling, Editor in Chief. Electronic News

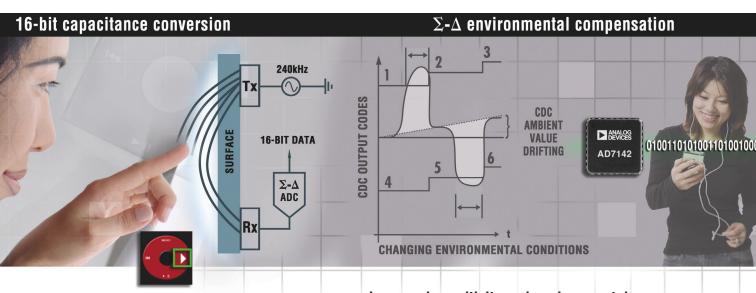

# 16-bit touch controller for the best user experience. In data conversion, analog is everywhere.

#### 16-bit $\Sigma$ - $\Delta$ CDC ...

- <1 femtofarad resolution</li>

- Full power mode: <1 mA

- Low power mode: 50 μA

- Shutdown current: <2 μA

- Supply voltage: 2.6 V to 3.6 V

- · Automatic environmental calibration

- · Automatic adaptive sensitivity

- SPI® or I2C® interface

- $\bullet$  32-lead 5 mm imes 5 mm LFCSP

- Price: \$1.65 (1k quantities)

#### ... enabling multiple applications

- · Consumer electronics

- · Medical instrumentation

- · Automotive applications

- · Industrial equipment

- PC peripherals

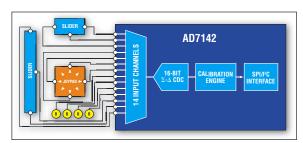

With 14 inputs, the AD7142 can be programmed for a variety of navigation functions including buttons, sliders, scroll wheels, and joypads.

# Improved sensitivity and environmental calibration—made possible by $\Sigma\text{-}\Delta$ conversion

For products with increasing feature convergence, finger-driven navigation enhances the user experience—for designers as well as consumers. The AD7142 capacitance-to-digital converter (CDC) with on-chip environmental compensation delivers unmatched touch control performance. It offers:

- · Reliable performance over supply and temperature

- · Programmable functionality and touch sensitivity

- 50% lower power than competitive solutions

- Development tools, such as reference designs and host software, that reduce time to market

ADI also offers CDC solutions for measuring proximity, position, level, pressure, and humidity.

#### New online seminar:

View the "Innovative Human Interface Design Techniques Using CDCs" seminar at <a href="https://www.analog.com/onlineseminar-CDC">www.analog.com/onlineseminar-CDC</a>.

The FHP3x50 family targets HD video.

#### AGLOBAL DESIGNER

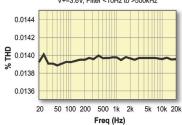

#### Video op amps exceed HD needs

The most recent incarnation of power-semiconductor supplier Fairchild Semiconductor brands itself the "power franchise." Now, discrete supplier Fairchild is re-entering the high-performance-op-amp arena with the FHP3x50 voltage-feedback-amplifier family for use in HD (high-definition) video products, such as set-top boxes. These amplifiers for videosignal chains address a market in which the company provides components such as video-filter drivers. Fairchild bases these parts on the new low-capacitance, complementary-bipolar-silicon-on-insulator BCP-6T process. Company officials claim that the process enables the amplifiers to deliver higher bandwidth, more output current, and better dc performance than competing products.

The FHP3x50's full-power bandwidth is 210 MHz at -3dB, and the chips have a 1100V/µsec slew rate and 0.07%/0.03° differential gain and phase error. Gain flatness of 0.1 dB extends to 50 MHz. and Fairchild officials say that pulse response is good with fast slewing edges and minimal preshoot, undershoot, or overshoot. Input-bias current is 0.05 mA, and the devices use 3.6 mA. Output-drive capability is ±55 mA. The chips are available in triple and quad packages.

For standard-definition sys-

tems, the fast rail-to-rail amplifiers of the FHP3x30 family come as singles, duals, and guads and offer unity-gain bandwidth of 170 MHz, driving  $\pm$  100-mA outputs.

Fairchild also claims competitive advantages in gain/ phase error, gain flatness, and pulse response over other devices of the same class. These devices suit use in video-signal chains and also work as general-purpose amplifiers. Prices range from 49 to 86 cents (1000).

-by Graham Prophet, **EDN Europe** Fairchild Semiconductor,

www.fairchildsemi.com.

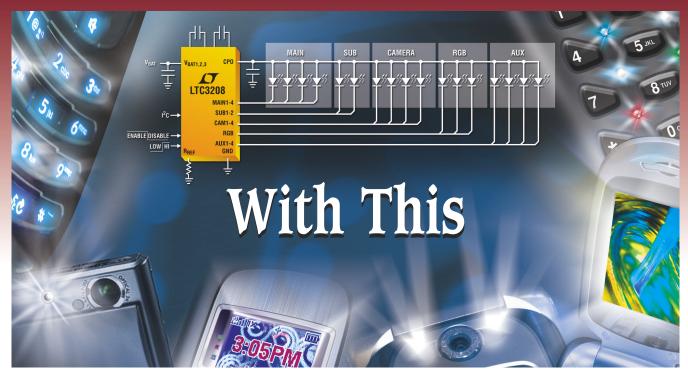

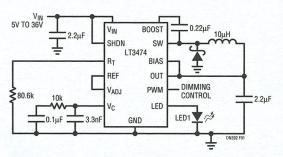

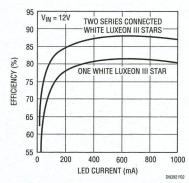

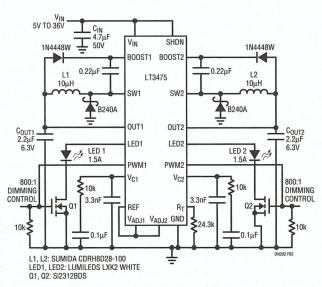

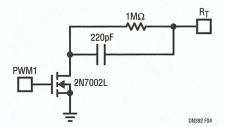

#### LEDs take over in "mood" lighting

Using tricolor arrays of LEDs, architects and lighting designers can fine-tune intensity, color, and pattern to achieve "mood" lighting and other effects. Designers need to ensure that they apply the correct drive to the LEDs, and they need to program the desired patterns into LED arrays.